|

|

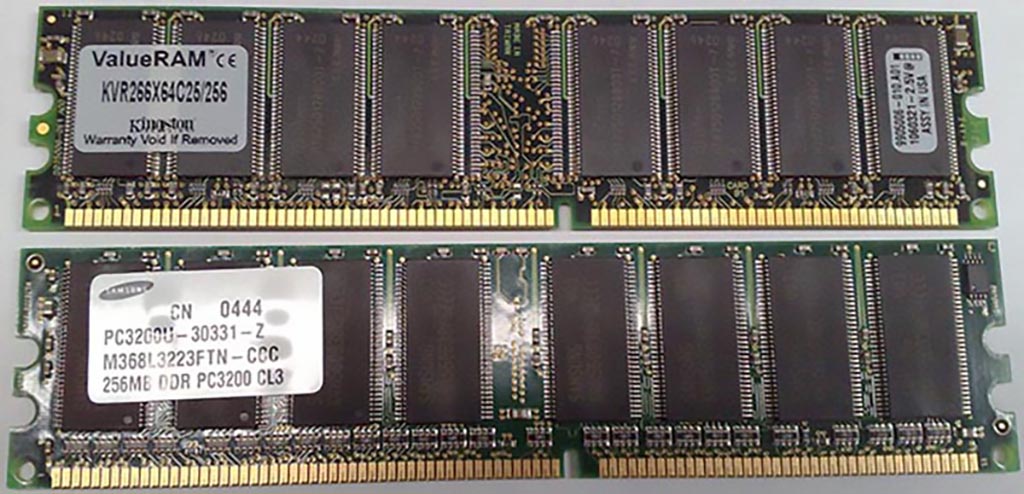

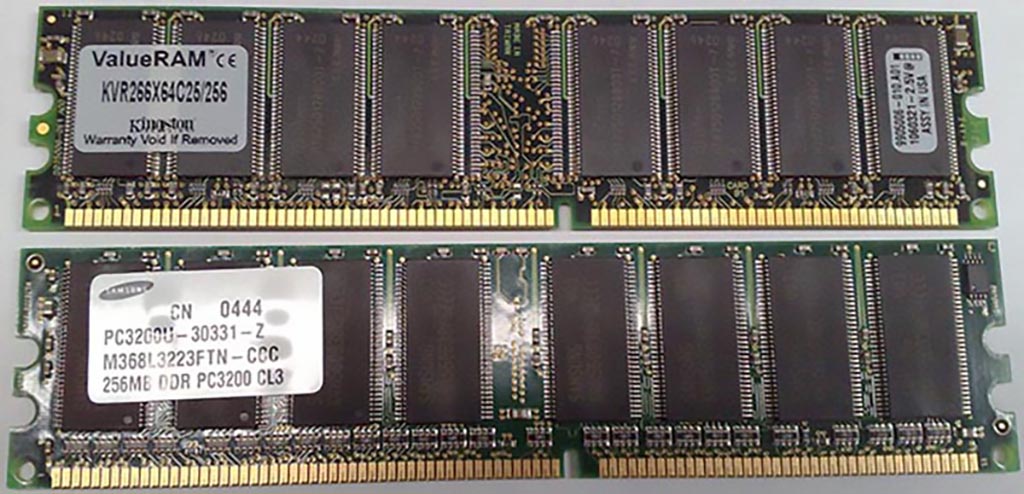

Double data rate synchronous dynamic random access memory (DDR SDRAM) is

a class of memory integrated circuits used in computers. DDR SDRAM

(sometimes referred to as DDR1 SDRAM).

Compared to single data rate (SDR) SDRAM, the DDR SDRAM interface makes

higher transfer rates possible by more strict control of the timing of the

electrical data and clock signals. Implementations often have to use schemes

such as phase-locked loops and self-calibration to reach the required timing

accuracy. The interface uses double pumping (transferring data on both the

rising and falling edges of the clock signal) to lower the clock frequency.

One advantage of keeping the clock frequency down is that it reduces the

signal integrity requirements on the circuit board connecting the memory to

the controller. The name "double data rate" refers to the fact that a DDR

SDRAM with a certain clock frequency achieves nearly twice the bandwidth of

a single data rate (SDR) SDRAM running at the same clock frequency, due to

this double pumping. With data being transferred 64 bits at a time, DDR

SDRAM gives a transfer rate of (memory bus clock rate) × 2 (for dual rate) ×

64 (number of bits transferred) / 8 (number of bits/byte). Thus, with a bus

frequency of 100 MHz, DDR SDRAM gives a maximum transfer rate of 1600 MB/s.

Sizes Mb ranged from 32Mb to 2Gb.

They were either Single Sided or Dual Sided.

Typical DDR SDRAM clock rates are 200, 266, 333 and 400MHz,

They had 184 pin connectors, and 1 notch |

| |

|