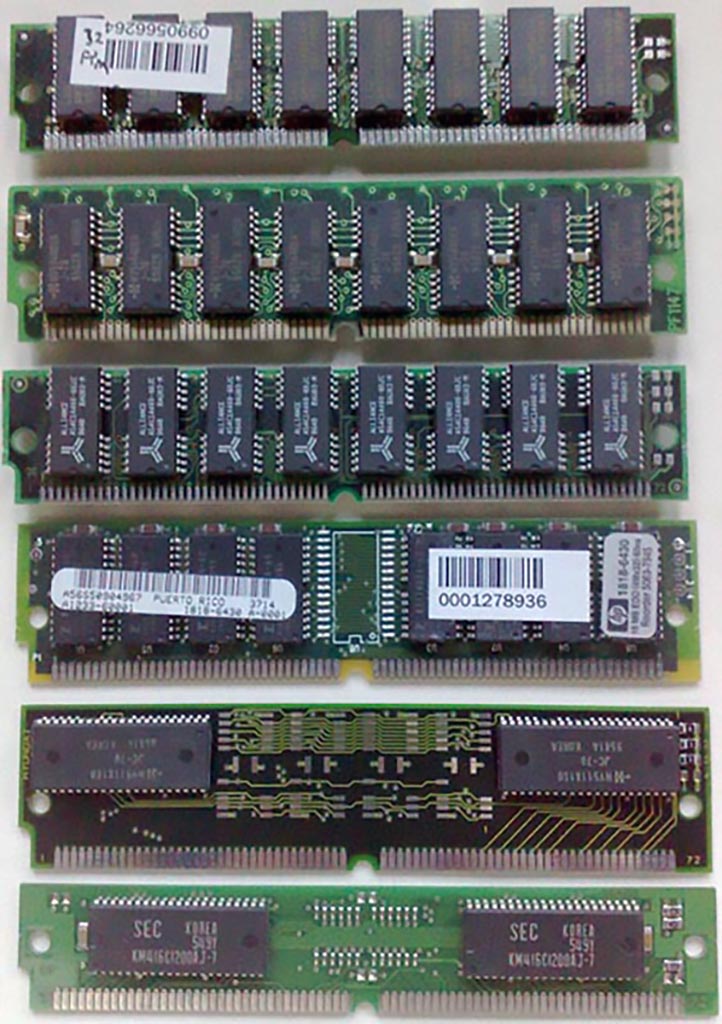

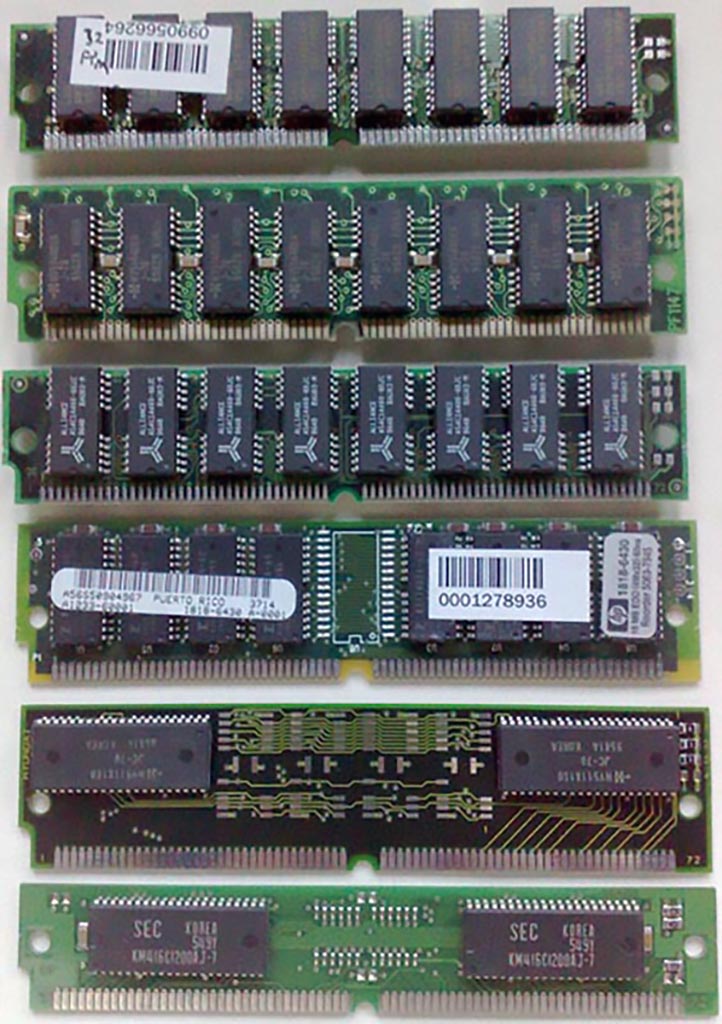

| SIMM RAM FPM and EDO RAM Fast page mode DRAM is also called FPM

DRAM, Page mode DRAM, Fast page mode memory, or Page mode memory.

In page mode, a row of the DRAM can be kept "open" by holding /RAS low

while performing multiple reads or writes with separate pulses of /CAS so

that successive reads or writes within the row do not suffer the delay of

precharge and accessing the row. This increases the performance of the

system when reading or writing bursts of data.

Static column is a variant of page mode in which the column

address does not need to be strobed in, but rather, the address inputs may

be changed with /CAS held low, and the data output will be updated

accordingly a few nanoseconds later.

Nibble mode is another variant in which four sequential locations

within the row can be accessed with four consecutive pulses of /CAS. The

difference from normal page mode is that the address inputs are not used for

the second through fourth /CAS edges; they are generated internally starting

with the address supplied for the first /CAS edge.

EDO DRAM, sometimes referred to as Hyper Page Mode enabled DRAM,

is similar to Fast Page Mode DRAM with the additional feature that a new

access cycle can be started while keeping the data output of the previous

cycle active. This allows a certain amount of overlap in operation

(pipelining), allowing somewhat improved performance. It was 5% faster than

Fast Page Mode DRAM, which it began to replace in 1995, when Intel

introduced the 430FX chipset that supported EDO DRAM.

To be precise, EDO DRAM begins data output on the falling edge of /CAS,

but does not stop the output when /CAS rises again. It holds the output

valid (thus extending the data output time) until either /RAS is deasserted,

or a new /CAS falling edge selects a different column address.

Single-cycle EDO has the ability to carry out a complete memory

transaction in one clock cycle. Otherwise, each sequential RAM access within

the same page takes two clock cycles instead of three, once the page has

been selected. EDO's performance and capabilities allowed it to somewhat

replace the then-slow L2 caches of PCs. It created an opportunity to reduce

the immense performance loss associated with a lack of L2 cache, while

making systems cheaper to build. This was also good for notebooks due to

difficulties with their limited form factor, and battery life limitations.

An EDO system with L2 cache was tangibly faster than the older FPM/L2

combination.

Single-cycle EDO DRAM became very popular on video cards towards the end

of the 1990s. It was very low cost, yet nearly as efficient for performance

as the far more costly VRAM.

Much equipment taking 72-pin SIMMs could use either FPM or EDO. Problems

were possible, particularly when mixing FPM and EDO. Early Hewlett-Packard

printers had FPM RAM built in; some, but not all, models worked if

additional EDO SIMMs were added.

Sizes Mb ranged from 1Mb to about 128Mb.

They were either Single Sided or Dual Sided.

They had 72 pin connectors and 1 notch. |